在处理器上的Cache是什么Cache()。A.L1 CacheB.动态 CacheC.处理增加 CacheD.RAM CacheE.系统 Cache

题目

A.L1 Cache

B.动态 Cache

C.处理增加 Cache

D.RAM Cache

E.系统 Cache

相似考题

更多“在处理器上的Cache是什么Cache()。 ”相关问题

-

第1题:

Pentium 4微处理器的L1 Cache包括两个部分,它们是指令Cache(ETC) Cache。

正确答案:数据

数据 -

第2题:

微处理器的性能指票不包括()。A 主频

B 字长

C 存取周期

D Cache 容量

正确答案:D

-

第3题:

如果应用程序需要的数据已经在内存中,称作()。

- A、Cache Read

- B、Cache Hit

- C、Cache Miss

- D、Cache Latch

正确答案:B -

第4题:

什么叫执行轨迹Cache?Intel公司在哪种微处理器中首次采用该种Cache?

正确答案: 执行轨迹Cache位于指令译码逻辑和执行核心逻辑之间,用来存放已经译码的指令或微操作。Intel公司在Pentium 4微处理器中首次采用了执行轨迹Cache。 -

第5题:

计算机中设置Cache的作用是什么?能否将Cache的容量扩大,最后取代主存,为什么?

正确答案: 计算机中设置Cache的作用是解决CPU和主存速度不匹配问题。

不能将Cache的容量扩大取代主存,原因是:

(1)Cache容量越大成本越高,难以满足人们追求低价格的要求;

(2)如果取消主存,当CPU访问Cache失败时,需要将辅存的内容调入Cache再由CPU访问,造成CPU等待时间太长,损失更大。 -

第6题:

在一个计算机系统中,下列说法正确的是()。

- A、主存的容量远大于Cache的容量,主存的速度比Cache快

- B、主存的容量远小于Cache的容量,主存的速度比Cache快

- C、主存的容量远大于Cache的容量,主存的速度比Cache慢

- D、主存的容量远小于Cache的容量,主存的速度比Cache慢

正确答案:C -

第7题:

解释Pentium微处理器的引脚信号CACHE和BRDY的定义。

正确答案: (1)CACHE,Cache控制信号,输出,低电平有效。CPU在读操作时,此控制信号为低电平,表示CPU正在从主存中读取数据到CPU内部的Cache中;当CPU进行写操作时,此信号为低电平,表示CPU内部Cache中修改过的数据正在写回到主存中。

(2)BRDY,突发就绪信号。输入,低电平有效,当其有效,表示外设已处于准备好状态,可以进行数据传输。如果此信号在连续多个周期内有效,则为突发传输状态。 -

第8题:

Cache的工作原理是什么?

正确答案:Cache也称为高速缓冲存储器和快存,它是介于CPU和主存之间的一个小容量存储器,其主要目的是为了解决CPU和主存速度不匹配的问题。它处于存储器层次结构的“CPU-主存”层次之间, 其内容是主存中最活跃、访问最频繁的数据的副本。当CPU要访问数据时先在cache查找,找到就使用,找不到再访问主存。使用Cache可以缩短平均内存访问时间。 -

第9题:

将CPU集成在一块芯片上所形成的元器件称为()。

- A、微处理器

- B、ROM

- C、CMOS

- D、Cache

正确答案:A -

第10题:

问答题增加Cache块大小,对Cache性能有何影响?其原因是什么?正确答案: (1)对给定的Cache容量,当块大小增加失效率开始是下降,后来反而上升了;

(2)Cache容量越大,使失效率达到最低的块大小就越大。

导致上述失效率先下降后上升的原因,在于增加块大小会产生双重作用。

一方面它减少了强制性失效,因为局部性原理有时间局部性和空间局部性两方面的含义,增加块大小利用了空间局部性;

另一方面,由于增加块大小会减少Cache中块的数目,所以有可能会增加冲突失效。在Cache容量较小时,甚至还会增加容量失效。

刚开始增加块大小时,由于块大小还不是很大,上述的第一种作用超过第二种作用,从而使失效率下降。但等到块大小较大时,第二种作用超过第一种作用,使失效率上升。解析: 暂无解析 -

第11题:

问答题计算机中设置Cache的作用是什么?能否将Cache的容量扩大,最后取代主存,为什么?正确答案: 计算机中设置Cache的作用是解决CPU和主存速度不匹配问题。

不能将Cache的容量扩大取代主存,原因是:

(1)Cache容量越大成本越高,难以满足人们追求低价格的要求;

(2)如果取消主存,当CPU访问Cache失败时,需要将辅存的内容调入Cache再由CPU访问,造成CPU等待时间太长,损失更大。解析: 暂无解析 -

第12题:

问答题某处理器包含一片内Cache,容量为8K字节,且采用4路组相联结构,块的大小为4个32位字。当Cache未命中时,以分组方式从主存读取4个字到Cache,假定主存容量为16MB。试说明:Cache共分为多少组?正确答案: 为求组数,先求行数

行数=Cache容量/块的大小//Cache容量:8KB=213B;

//块的大小:4*32bit=2bit=24B

=213/24=29

组数=行数/每组行数//因4路相联,所以每组4行

=29/4=27

所以,组数为128个。解析: 暂无解析 -

第13题:

下面关于Cache的叙述,“(6)”是错误的。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是动态更新的

C.使用Cache存储器并不能扩大主存的容量

D.Cache的命中率只与其容量相关

正确答案:D

解析:本题考查高速缓存基础知识。高速缓存Cache有如下特点:它位于CPU和主存之间,由硬件实现;容量小,一般在几KB到几MB之间;速度一般比主存快5到10倍,由快速半导体存储器制成;其内容是主存内容的副本,对程序员来说是透明的;Cache既可存放程序又可存放数据。Cache存储器用来动态存放主存的部分拷贝(副本)。控制部分的功能是:判断CPU要访问的信息是否在Cache存储器中,若在即为命中,若不在则没有命中。命中时直接对Cache存储器寻址。未命中时,若是读取操作,则从主存中读取数据,并按照确定的替换原则把该数据写入Cache存储器中:若是写入操作,则将数据写入主存即可。Cache的命中率主要与如下几个因素有关:程序在执行过程中的地址流分布情况;当发生Cache块失效时,所采用的替换算法;Cache的容量;在组相联映像方式中,块的大小和分组的数目;所采用的Cache预取算法等等。Cache的命中率随其容量增加而提高,它们之间的关系曲线如下图所示。在Cache容量比较小的时候,命中率提高的非常快,随着Cache容量的增加,命中率提高的速度逐渐降低。当Cache容量增加到无穷大时,命中率可望达到100%,但这是实际上是做不到的。

-

第14题:

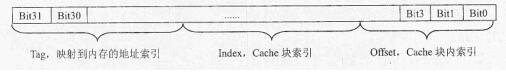

某32位总线处理器的Cache直接映射方式如下图所示,若Cache大小为16KB,每个Cache块为16字节,则Offset,Index和Tag所占的位数分别是( )。 A.4,10,18

A.4,10,18

B.4,12,16

C.5,10,17

D.5,12,15答案:A解析:本题考查嵌入式处理器Cache的基础知识。Cache是一种高速缓冲储存器,它的主要作用是提高CPU数据输入的速率,调和CPU速度与内存存储之间的巨大差异。通俗一点说就是CPU太快,内存速度相对较慢,而Cache的速度快,但是Cache的价格比较昂贵。很容易想到的一个办法就是利用小容量Cache在CPU和内存中间当桥梁,也就是说把CPU在下一个时间段需要用到的数据提前存入Cache中,当CPU需要的时候可以快速的从Cache中取得数据,这样就可以在一定程度上提高计算机的性能。但怎样才能知道CPU在下一个时间段需要用到内存中的那些数据呢?局部性原理就可以解决这个问题。使用Cache改善系统性能的依据就是局部性原理。局部性原理反映在计算机中就是如果CPU当前时间用到内存中某块数据,那么CPU在下一个时间段内用到这块数据周围的数据可能性就非常大。Cache即是按照这种原理,把这个时间段中CPU用到 的这块数据周围的数据存入Cache中为下一个时间段的CPU使用做准备,这样当下一个时间段的CPU需要数据了就可以直接从储存较快的Cache中取得需要的数据,这样自然就可以提高计算机的性能。另外涉及到的一个问题是Cache中的数据和内存中的部分数据是一致的,那么当CPU从Cache取得数据后怎样知道这块数据在内存中的具体地址呢?于是想到了映射的方法,将Cache中的数据按照特定的方式和内存中的数据进行映射,这样CPU就很容易找到Cache中数据在内存中的真实位置了。映射的方式目前有三种,分别是直接映射,全相连映射和组相联映射。直接映射最为简单,即是指主存中的一个字块只能映射到Cache中一个准确确定的字块。全连接映射是指主存中的一个字块可以映射到Cache中的任何一个字块。组相连映射是上述两种方式的折中连接。在上图所示的直接映射中,如果每个Cache块的字节数是16,则Cache块内索引的位数为4;如果Cache的大小为16KB,则其Index索引的位数为10位,映射到内存的地址位数为32-4-10=18。 -

第15题:

增加Cache块大小,对Cache性能有何影响?其原因是什么?

正确答案: (1)对给定的Cache容量,当块大小增加失效率开始是下降,后来反而上升了;

(2)Cache容量越大,使失效率达到最低的块大小就越大。

导致上述失效率先下降后上升的原因,在于增加块大小会产生双重作用。

一方面它减少了强制性失效,因为局部性原理有时间局部性和空间局部性两方面的含义,增加块大小利用了空间局部性;

另一方面,由于增加块大小会减少Cache中块的数目,所以有可能会增加冲突失效。在Cache容量较小时,甚至还会增加容量失效。

刚开始增加块大小时,由于块大小还不是很大,上述的第一种作用超过第二种作用,从而使失效率下降。但等到块大小较大时,第二种作用超过第一种作用,使失效率上升。 -

第16题:

Cache命中时间往往会直接影响到处理器的时钟频率。

正确答案:正确 -

第17题:

某处理器包含一片内Cache,容量为8K字节,且采用4路组相联结构,块的大小为4个32位字。当Cache未命中时,以分组方式从主存读取4个字到Cache,假定主存容量为16MB。试说明:Cache共分为多少组?

正确答案:为求组数,先求行数

行数=Cache容量/块的大小//Cache容量:8KB=213B;

//块的大小:4*32bit=2bit=24B

=213/24=29

组数=行数/每组行数//因4路相联,所以每组4行

=29/4=27

所以,组数为128个。 -

第18题:

简述微处理器内部Cache的发展变化情况。

正确答案:Cache在刚引入时,是指在CPU与主存之间容量相对较小、但速度很快的存储器。早期的Cache一般由静态RAM(SRAM)构成。然而,SRAM的速度和CPU的速度还是相差甚远。为了进一步提高访问存储器操作的执行速度,从80486开始,在CPU内部设置Cache。并且,由80486的一个Cache变成分别存放数据和指令的两个Cache;内部Cache的容量也由80486的8KB逐步扩大到256 KB或更多;Cache的组织由直接相联变成多路组相联;CPU内部的Cache也由一级变为两级,并且Cache的存取时间变得更短。前3方面变化使得Cache的命中率得到进一步提高,而第4方面变化使得CPU访问存储器的操作进一步加快。 -

第19题:

Cache是什么意思?

正确答案:高速缓冲存储器Cache是处理器与主存之间速度很快但容量较小的存储器。 -

第20题:

在PC机中,各类存储器的速度由高到低的次序是()。

- A、主存、Cache、硬盘、软盘

- B、硬盘、Cache、主存、软盘

- C、Cache、硬盘、主存、软盘

- D、Cache、主存、硬盘、软盘

正确答案:D -

第21题:

在处理器上的Cache是什么Cache()。

- A、L1 Cache

- B、动态 Cache

- C、处理增加 Cache

- D、RAM Cache

- E、系统 Cache

正确答案:A -

第22题:

问答题假定有三个处理器,分别带有以下不同的cache:cache1:采用直接映射方式,块大小为1个字,指令和数据的缺失率分别为4%和6%;cache2:采用直接映射方式,块大小为4个字,指令和数据的缺失率分别为2%和4%;cache3:采用2-路组相联映射方式,块大小为4个字,指令和数据的缺失率分别为2%和3%。在这些处理器上运行相同的程序,该程序的CPI为2.0,其中有一半是访存指令。若缺失损失为(块大小+6)个时钟周期,处理器1和处理器2的时钟周期都为420ps,带有cache3的处理器3的时钟周期为450ps。请问:哪个处理器因cache缺失而引起的额外开销最大?哪个处理器执行速度最快?正确答案: 假设所运行的程序共执行N条指令,每条访存指令仅读写一次内存数据,则在该程序执行过程中各处理器因cache缺失而引起的额外开销和执行时间计算如下。

对于处理器1:额外开销为:N×4% + 6%×50%)×(1+6)=0.49 N个时钟周期

执行程序所需时间为:(N×2.0 +0.49N)×420ps = 1045.8N ps

对于处理器2:额外开销为:N×(2%+4%×50%)×(4+6)=0.40N个时钟周期

执行程序所需时间为:(N×2.0+0.40N)×420ps=1008N ps

对于处理器3:额外开销为:N×(2%+3%×50%)×(4+6)=0.35N个时钟周期

执行程序所需时间为:(N×2.0+0.35N)×450ps=1057.5N ps

由此可见,处理器1的cache缺失引起的额外开销最大,处理器2的执行速度最快。解析: 暂无解析 -

第23题:

单选题在处理器上的Cache是什么Cache()。AL1 Cache

B动态 Cache

C处理增加 Cache

DRAM Cache

E系统 Cache

正确答案: C解析: 暂无解析