13、四个全加器可以组成一个串行进位的四位数加法器()

题目

13、四个全加器可以组成一个串行进位的四位数加法器()

相似考题

更多“13、四个全加器可以组成一个串行进位的四位数加法器()”相关问题

-

第1题:

并行加法器的全加器个数和操作位数相同。()此题为判断题(对,错)。

正确答案:正确

-

第2题:

串行加法器只需要一位全加器就行了。()此题为判断题(对,错)。

参考答案:正确

-

第3题:

加法器有串行进位和()进位之分。参考答案:超前

-

第4题:

影响加法器运算速度的主要因素是(5)。

A.组成全加器的元器件的工作速度

B.串行进位链的总延迟时间

C.所有本地进位di产生的速度

D.所有全加和Qi产生的速度

正确答案:B

解析:本题考查加法器的组成。加法器的主要功能是对数进行加法运算,在大多数的中央处理器中,很多其他计算也是经过变换后使用加法器来完成的,一个位加法的逻辑图如下图所示。在上图中,Xi、Yi是加数和被加数;Ci+1是低位进位;Ci是进位;Zi是和。在加法运算器进行运算时,第f位的和除与本位操作数Xi和Yi有关外,还依赖.于低位进位信号,而低位进位信号依赖于更低位的进位信号,而这样的进位逻辑就是串行进位链。因此影响加法器运算速度的主要因素是串行进位链的总延迟时间,而加法器本身求和的延迟时间反而是次要的。 -

第5题:

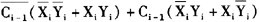

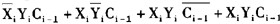

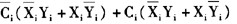

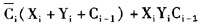

全加器是由两个加数Xi和Yi以及低位来的进位Ci-1作为输入,产生本位和S,以及向高位的进位Ci的逻辑电路。(51)和(52)分别是Si和Ci的正确逻辑表达式。全加器亦可通过半加器来实现,此时Si=(53)。若某计算机采用8位带符号补码表示整数,则可由8个全加器(i=1,2,……8,i=8为最高位,即符号位)串接构成8位加法器,C0=0。该加法器有一个状态寄存器,记录运算结果的状态。其中,N和V分别表示符号位与溢出标志位,则其逻辑表达式分别为(54)和(55)。

A.

B.

C.

D.

正确答案:D

正确答案:D

解析:本位和为1可以分解为:当两加数与低进位均为1的情况(Xi+Yi+Ci-1);当没有进位产生时,两加数、低进位有一个为1的情况Ci(Xi+Yi+Ci-1)。本位进位为1即两加数、低进位同时最少有两个为1的情况,即XiYi+XiCi-1+YiCi-1。半加器异或的作用,Si可表示为两加数、低进位三者若有两个相同,则Si为1,即Xi⊕C⊕i-1Yi。8位加法器中,若C7为0,则符号位由X8.Y8决定,进行异或即可,或表示为x8+y8。若C7为1,则可表示成+x8y8,即C7(+x8y8)+(x8+y8)。若C8=1,表示符号位运算产生进位,此时若C7=0,表示低位没有进位,说明是两加数的符号位运算产生了进位,则结果符号位必然不同于两加数的符号,产生溢出;否则,没有溢出。若C8=0,表示c7,x8,y8,最多有一个是1,若C7=1,说明符号位改变,产生溢出。这种情况可以用半加表示,即C7.C8。 -

第6题:

下列关于加法器的说法错误的是()。A.实现n位的串行加法器只需1位全加器

B.实现n位的并行加法器需要n位全加器

C.影响并行加法器速度的关键固素是加法器的位数的多少

D.加法器是一种组合逻辑电路答案:C解析:n位的并行加法器有n位的全加器,可同时对数据的各位相加,但低位运算所产生的进位会影响高位的运算结果,所以并行加法器的运算时间主要由进位信号的传递时间决定,而不是加法器位数的多少,选C项。 -

第7题:

串行加法器只需要一位全加器就行了。

正确答案:正确 -

第8题:

加法器采用并行进位的目的是()。

- A、提高加法器的速度

- B、快速传递进位信号

- C、优化加法器结构

- D、增强加法器功能

正确答案:B -

第9题:

半加法器和全加法器的区别是()。

- A、是否产生进位

- B、是否处理以前的进位

- C、是否产生和位

- D、是否处理以前的和位

正确答案:B -

第10题:

判断题串行加法器只需要一位全加器就行了。A对

B错

正确答案: 对解析: 暂无解析 -

第11题:

单选题串行加法器包含()个全加器。A1

B2

C3

D4

正确答案: D解析: 暂无解析 -

第12题:

单选题加法器采用并行进位的目的是()。A提高加法器的速度

B快速传递进位信号

C优化加法器结构

D增强加法器功能

正确答案: D解析: 暂无解析 -

第13题:

前进位加法器比串行进位加法器速度慢。()此题为判断题(对,错)。

参考答案:错误

-

第14题:

74182芯片是一个()的进位链集成电路。A、先行进位

B、后行进位

C、串行进位

D、无进位

参考答案:A

-

第15题:

既考虑低位进位,又考虑向高位进位,应选应

A、全加器

B、半加器

C、全减器

D、半减器

参考答案:A

-

第16题:

全加器是由两个加数Xi和Yi以及低位来的进位Ci-1作为输入,产生向高位的进位Ci以及本位利Si的逻辑电路。(65)和(66)分别是进位和本位和的正确逻辑表达式。全加器亦可通过半加器来实现,此时Si=(67)。若某计算机采用8位带符号补码表示整数,则可由8个全加器(i =1,2,……8,i=8为最高位,即符号位)串接构成8位加法器,CO=0。该加法器有一个状态寄存器,记录运算结果的状态。其中,N和V分别表示符号位与溢出标志位,则其逻辑表达式分别为(68)和(69)。

A.XiYi+XiCi-1+YiCi-1

B.XiYi+XiSj+YiSi

C.XiYi+XiCi-1+YiCi-1

D.(XiYi+XiYi).Ci-1

正确答案:C

-

第17题:

在串行进位的并行加法器中,影响加法器运算速度的关键因素是()。A.门电路的级延迟

B.元器件速度

C.进位传递延迟

D.各位加法器速度的不同答案:C解析:加法器是整个运算器的核心,提高加法器的运算速度最直接的方法就是多位并行加法。本题中4个选项均会对加法器的速度产生影响,但只有进位传递延迟对并行加法器的影响最为关键。 -

第18题:

下列不属于组合逻辑电路的加法器为()。

- A、半加器

- B、全加器

- C、多位加法器

- D、计数器

正确答案:D -

第19题:

串行加法器包含()个全加器。

- A、1

- B、2

- C、3

- D、4

正确答案:A -

第20题:

乘法器的硬件结构通常采用()

- A、串行加法器和串行移位器

- B、并行加法器和串行左移

- C、并行加法器和串行右移

- D、串行加法器和串行右移

正确答案:C -

第21题:

与4位串行进位加法器比较,使用超前进位全加器的目的是()。

- A、完成自动加法进位

- B、完成4位加法

- C、提高运算速度

- D、完成4位串行加法

正确答案:C -

第22题:

单选题74182芯片是一个()的进位链集成电路。A先行进位

B后行进位

C串行进位

D无进位

正确答案: D解析: 暂无解析 -

第23题:

单选题A8位并行加法器

B8位串行加法器

C4位并行加法器

D4位串行加法器

正确答案: D解析: -

第24题:

单选题与4位串行进位加法器比较,使用超前进位全加器的目的是()。A完成自动加法进位

B完成4位加法

C提高运算速度

D完成4位串行加法

正确答案: C解析: 暂无解析